As some of you may already know that Arm’s Big.Little heterogeneous multi-core CPU technology has been quite successful in Google Android-based smartphones. Intel plans to implement similar hybrid CPU core architecture with its upcoming Desktop PC Alder Lake-S CPU lineup, which is going to land up next year.

AMD on the other hand already filed a patent before for hybrid processors dating as far back as 2017, but the company has no plans to bring this hybrid multi-core CPU architecture to the market unless the operating systems for PCs can fully utilize it, and there’s a noticeable improvement in doing so.

AMD won’t follow suit, and the company says it is waiting until the time and the software is right before it brings a similar hybrid CPU core topology.

Patent: Instruction subset implementation for low power operation – AMD

Basically, AMD BIG.little.

This patent still in the adjustment process.

More Details: https://t.co/7pPd3NSXj2 pic.twitter.com/pN5OiHi4BS

— Underfox (@Underfox3) August 8, 2020

AMD continues to study hybrid CPU architectures though, but according to Joe Macri, VP and Product Chief Technology Officer at AMD, the company has no plans to design a hybrid CPU chip, at least not before the operating system/OS gets an appropriate scheduler and a memory allocator.

“We’ve been studying Big.Little,” said Joe Macri, during an engineering roundtable. “It’s been 15+ years, so this is not a new concept in any way shape or form. We continue to study it, we continue to look at it. We’re not going to talk about whether we’ll do it or not, but I’m going to talk about some of the challenges of it and around what you really want to do with it. Is the goal power efficiency?

Is the goal more performance? Is the goal just marketing, ‘I want more core count’, regardless of what it does for the other two variables? […] We’re not going to do it just to have a bigger number.”

“Just driving up the core count with little isn’t going to be that useful until software comes along.”

A heterogeneous multi-core CPU technology speeds the transfer of threads between high-performance cores and smaller low-performance cores in a big.LITTLE-esque hybrid computing architecture. As mentioned before AMD has already filed a similar patent, but as with all patent filings, this doesn’t assure that AMD will bring a hybrid computing device to the market.

Though, the company is certainly busy researching and studying hybrid CPU architectures. The patent outlines a new instruction set implementation for low power tasks and operations.

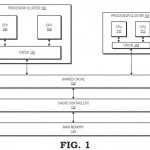

AMD’s patent clearly describes an implementation that allows for one subset of instructions to execute on larger full-featured processing cores optimized for higher performance, while a second subset of instructions to run on smaller simplified cores designed for power efficiency.

The patent outlines a method for the cores to use a shared memory location to speed the transfer of threads, based upon certain variables, between the two types of cores.

Arm’s Big.Little heterogeneous multi-core design uses high-performance ‘Big’ cores for demanding and heavy tasks (heavy performance-sensitive workloads), and low-power ‘little’ or small cores for light and simple background tasks. The general concept of big.LITTLE has largely been to increase performance while minimising the overall power consumption. When a core isn’t busy, it could be shut off, thus improving power consumption further.

Intel has already forged ahead with a hybrid design with its Lakefield chips, but unlocking maximum efficiency and potential still requires the operating system/OS and applications to be aware of the architecture so they can target threads to the correct cores.

Building around such architecture having general-purpose cores basically involves a lot of variables, and most importantly the Operating system/OS needs to learn how to properly schedule all the tasks, and allocate memory for different types of cores to enhance the user experience, and optimize the overall performance.

Furthermore, programs also have to seamlessly switch from one type of cores to another, depending on the type of workload.

“Over time I think there will be a point when we are going to need ‘little,’ and it will be a point in time when the OS has the right attributes, the right capabilities in its scheduler and memory allocator, we’ll have the right memory subsystem,” said Joe Macri. “We’ll be able to give you not just a little bit better experience, but a much better experience. If we can’t get that experience change to be noticeable, why do it?”

“If you look at a scheduler—this is any schedule, I don’t care if you’re scheduling planes, trains, or computers—the most important attribute a scheduler wants to see is symmetry,” Macri continues.

“Just driving up the core count with little isn’t going to be that useful until software comes along,” said Macri. “It’s not a simple problem, and I think there’s been at least one company who has got it right. I wouldn’t say all the companies have got it right that have started doing it. What we’re really fighting, for Big.Little with AMD, is that Mike [Papermaster’s] team is doing such a great job with Big, it makes it hard to win with Little.”

AMD is already aware of the importance of OS schedulers. Back in the old days the company’s FX-series processors based on the Bulldozer microarchitecture were limited in performance because of the Windows’s scheduler.

AMD had to work with Microsoft to get everything right to improve the CPU’s performance; though even an optimized scheduler did not help Bulldozer compete with Intel’s offerings.

AMD officially has no plans to bring low-power ‘little’ cores in its CPU lineup yet, and AMD’s current CPU roadmap paints a totally different picture. If there’s a company with enough software engineers and expertise to deliver a fully working x86 hybrid CPU design right now, it’s Intel.

There has always been a dilemma regarding the efficiency when it comes to low-power vs. high-performance CPU cores. The method described in AMD’s patent allows the processor to independently sort out which type of thread should run on each cluster based on the instructions supported by the cores within. The threads could also shift between the cores based on the overall utilization.

For example, if the large or Big core is underutilized, the CPU would shift the thread to the small core (provided it supports the instruction set). And if the small core is over-utilized, the thread would shift to the larger core (once again, provided it supports the instructions).

This approach helps reduce or nullify the need for OS intervention for some types of thread movement patterns. The patent also explains an example wherein the clusters of cores could be CPUs, GPUs, or even DSPs.

Intel uses multiple stacked dies with its Foveros 3D stacking die-to-die interface, but this type of advanced 3D packaging tech is not necessarily required for a hybrid design. If AMD releases a hybrid computing design, it could come as one large die or an MCM design that might leverage many of the fundamental and basic concepts behind its existing CPU architectures.

However, as with all patents, AMD’s filing doesn’t guarantee that we will see new chips based on this hybrid technique. Nonetheless, the filing certainly shows that AMD is actively researching its own type of hybrid CPU core implementation.

Stay tuned for more!

Hello, my name is NICK Richardson. I’m an avid PC and tech fan since the good old days of RIVA TNT2, and 3DFX interactive “Voodoo” gaming cards. I love playing mostly First-person shooters, and I’m a die-hard fan of this FPS genre, since the good ‘old Doom and Wolfenstein days.

MUSIC has always been my passion/roots, but I started gaming “casually” when I was young on Nvidia’s GeForce3 series of cards. I’m by no means an avid or a hardcore gamer though, but I just love stuff related to the PC, Games, and technology in general. I’ve been involved with many indie Metal bands worldwide, and have helped them promote their albums in record labels. I’m a very broad-minded down to earth guy. MUSIC is my inner expression, and soul.

Contact: Email