Intel’s next generation of Alder Lake-S Core processors are said to be the company’s first 10nm mainstream desktop processors, and we have already seen documents, datasheets, and release notes for these CPUs which also appeared on Intel’s own developer website. These processors have been confirmed to support a new LGA1700 socket.

Alder Lake-S will be the first Intel architecture to offer ARM’s big.LITTLE approach to desktop processors. These next-gen CPUs are also expected to support the DDR5 memory and PCIe 4.0 interface.

The LGA1700 socket will have support for at least three generations of Intel CPUs. I’ve talked about Alder Lake CPUs before in my previous articles based on rumors and speculation, but now we have some solid evidence to back it up.

A recent leak from Zhihu coming via Videocardz has lent some serious evidence to the past rumors indicating that Intel is planning to introduce the big.LITTLE hybrid design similar to ARM, for its next-gen Alder Lake-S processors.

Intel’s Lakefield processors already feature the ‘Foveros stacking hybrid technology’. These are ultra low-power processors for thin and compact devices. It has been rumored before that the Alder Lake-S lineup of desktop processors will also feature a similar hybrid technology. Alder Lake-S would feature an 8+8 core configuration, in which half the cores are going to be ‘Big Cores’ and the remaining would be ‘Small Cores’. These processors would thus feature a total of 16 cores.

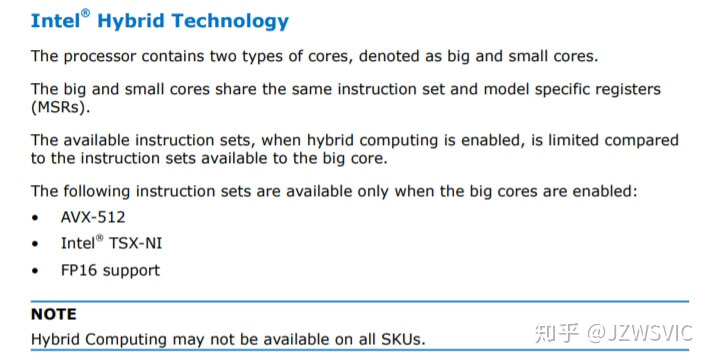

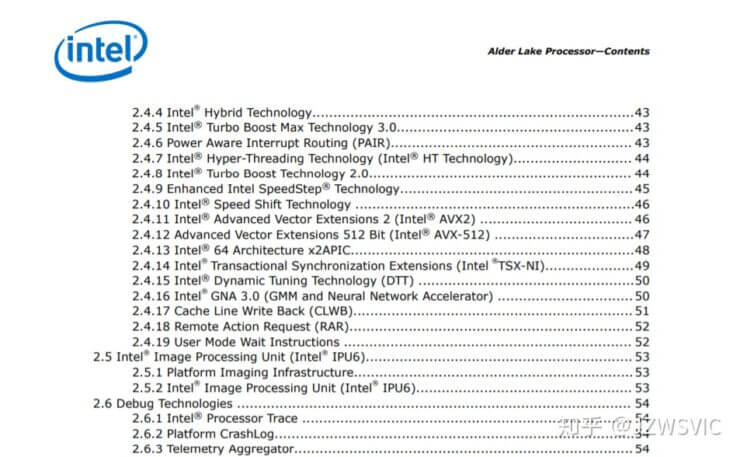

According to the new leak from Zhihu, the new hybrid Technology in Alder Lake architecture would allow both cores (small and big) to share the same instruction set and registers, but the availability of certain instructions would depend on which core is actually enabled and active. The user has also shared a screenshot from Intel’s internal documents which suggests that the following AVX-512, TSX-NI, and FP16 instructions will be disabled when the Hybrid Technology is enabled (both Big and Small cores are enabled at the same time).

The instructions will only work when the technology is disabled, which means the ‘Small’ cores are disabled. By disabled we can think of the processor’s mode/PL state, though we need more technical info to confirm how this will work on Desktop PCs.

Both the big and small cores will have the same instruction sets and model-specific registers, but will have different computational powers, and the overhead will also differ. We can assume the big cores to have higher throughput and clock speeds, whereas the small cores are going to be more power efficient. Like I have mentioned above, the following instruction sets AVX512, Intel TSX and FP16 are only going to work on the Big cores.

The ARM’s Big/Small core architecture makes more sense for mobile devices, to conserve power, but we still don’t know how this Hybrid technology is going to work on Desktops. The official PDF file detailing Intel’s hybrid technology can be viewed here.

Hello, my name is NICK Richardson. I’m an avid PC and tech fan since the good old days of RIVA TNT2, and 3DFX interactive “Voodoo” gaming cards. I love playing mostly First-person shooters, and I’m a die-hard fan of this FPS genre, since the good ‘old Doom and Wolfenstein days.

MUSIC has always been my passion/roots, but I started gaming “casually” when I was young on Nvidia’s GeForce3 series of cards. I’m by no means an avid or a hardcore gamer though, but I just love stuff related to the PC, Games, and technology in general. I’ve been involved with many indie Metal bands worldwide, and have helped them promote their albums in record labels. I’m a very broad-minded down to earth guy. MUSIC is my inner expression, and soul.

Contact: Email