In a surprise move AMD has recently filed a patent for a hybrid computing approach similar to ARM’s big.LITTLE technique and CPU design, in which high performance cores are paired with power efficient low-power smaller cores. This was spotted by tipster @Underfox3, and more details of this patent can be found here.

This is similar to ARM’s hybrid computing architecture in which this technique can speed up the transfer of threads between high-performance cores and smaller low-performance cores. Though, this patent filing does not necessarily mean that AMD is going to release a new hybrid computing device to the market anytime soon, but the company is most definitely experimenting with this hybrid technique. In future we might see a similar design from AMD as well, but for now things are only on paper.

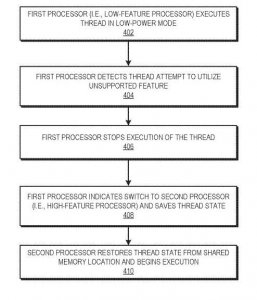

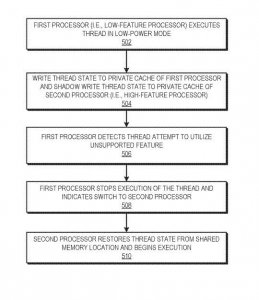

According to the patent a new instruction set (subset) for low power operations has been outlined, and this new implementation will allow a single subset of instructions to execute on the big processing cores which are optimized for higher performance, whereas a second subset of instructions can run on the smaller cores which are designed for power efficiency. According to the patent, there is a technique which can help the cores to use a ‘shared memory’ location to speed up the transfer of threads. But this will depend on certain variables.

Practically we expect the big cores to execute high performance workloads, while the smaller cores to execute lighter tasks. When a core is no longer in use or it is in idle state, it can be shut off, which will further help improve the power consumption of the device. Intel has already implemented a hybrid design with its ‘Lakefield’ chips, but similar to ARM, the operating system/OS and applications need to be aware of this hybrid architecture so that it can target and assign threads to the proper and correct cores. Intel uses multiple stacked dies with its Foveros 3D stacking technology.

AMD’s patent method appears to allow the processor to independently sort which type of thread should run on each of the clusters, but depending on the instruction sets supported by the corresponding cores (big+small). We can expect the threads to shift and rotate between both the cores depending on the utilization. For example, if the larger core is not fully utilized then the processor could shift the thread to the smaller core, provided the instructions are supported by it. In a similar fashion suppose the smaller core is over utilized, then we can expect the thread to shift to the larger processing core.

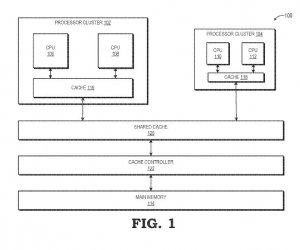

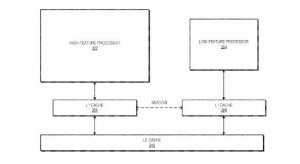

The concept is fundamentally the same as ARM’s technique, in which the bigger processor and the smaller core processor both have their own L1 Cache, but they share access to the high speed L2 cache. The smaller low feature processor implements a sub-set of the ISA features and operates at a low power/performance level than the bigger processor. It would be interesting to see how AMD implements this in the x86 CPU space. My guess is that this design will be first exclusive to mobility devices like notebooks, rather than desktops.

This hybrid technique actually reduces the need for the OS intervention for some types of thread movements, which can be useful in select applications, and it can reduce the overhead. The patent also gives an example wherein the clusters of cores could be CPUs, GPUs, or even DSPs. If AMD releases a similar hybrid computing design, then it could come as one large die, or the company can go for the MCM design approach as well.

The patent is still in the early development phase, so it is subject to change. Regardless, the filing certainly shows that AMD is experimenting with its own hybrid CPU design.

Hello, my name is NICK Richardson. I’m an avid PC and tech fan since the good old days of RIVA TNT2, and 3DFX interactive “Voodoo” gaming cards. I love playing mostly First-person shooters, and I’m a die-hard fan of this FPS genre, since the good ‘old Doom and Wolfenstein days.

MUSIC has always been my passion/roots, but I started gaming “casually” when I was young on Nvidia’s GeForce3 series of cards. I’m by no means an avid or a hardcore gamer though, but I just love stuff related to the PC, Games, and technology in general. I’ve been involved with many indie Metal bands worldwide, and have helped them promote their albums in record labels. I’m a very broad-minded down to earth guy. MUSIC is my inner expression, and soul.

Contact: Email